Informtica

Redação do Site Inovação Tecnológica – 31/05/2024

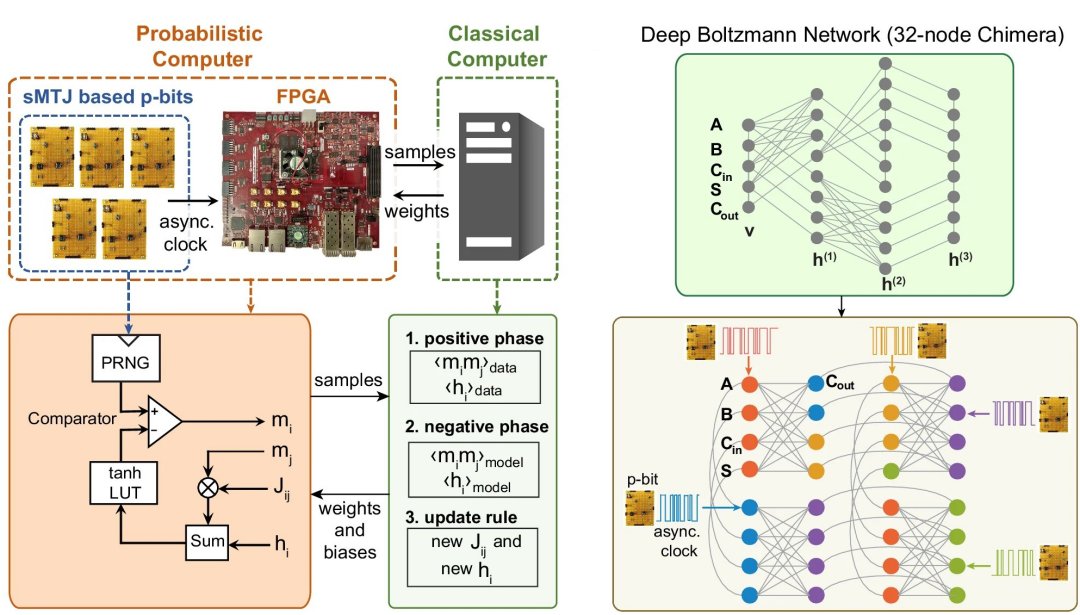

Esquema dos p-bits e fotos do prottipo de computador probabilstico.

[Imagem: Nihal Sanjay Singh et al. – 10.1038/s41467-024-46645-6]

Processador probabilstico

Uma equipe das universidades da Califrnia de Santa Brbara (EUA) e Tohoku (Japo) prossegue firme em sua proposta de criar um computador probabilstico que possa ser implementado na prtica.

Um computador probabilstico, ou p-computador, usa blocos de construo naturalmente aleatrios, chamados bits probabilsticos, ou p-bits. Ao contrrio dos bits dos computadores tradicionais, que precisam ter valores definidos (0 ou 1), os p-bits no tm um valor especfico, eles oscilam entre os valores.

Alm de gastar muito menos energia, essa arquitetura particularmente adequada para problemas como inferncia e amostragem, o que significa uma capacidade inata de resolver com eficincia vrias tarefas computacionalmente difceis em aprendizado de mquina e inteligncia artificial.

No ano passado, a equipe havia apresentado uma verso do seu p-computador usando componentes spintrnicos. Agora eles deram um passo rumo a tornar a arquitetura mais prxima de poder ser fabricada em escala industrial.

O novo prottipo combina um circuito semicondutor de xido metlico complementar (CMOS), o padro industrial atual, com um pequeno nmero de nanoms, criando um computador probabilstico heterogneo. Embora ainda no estejam inseridos nas linhas de produo atuais, os nanoms no tm impedimentos significativos para chegar l, s sendo necessrio um bom motivo para fabric-los em srie.

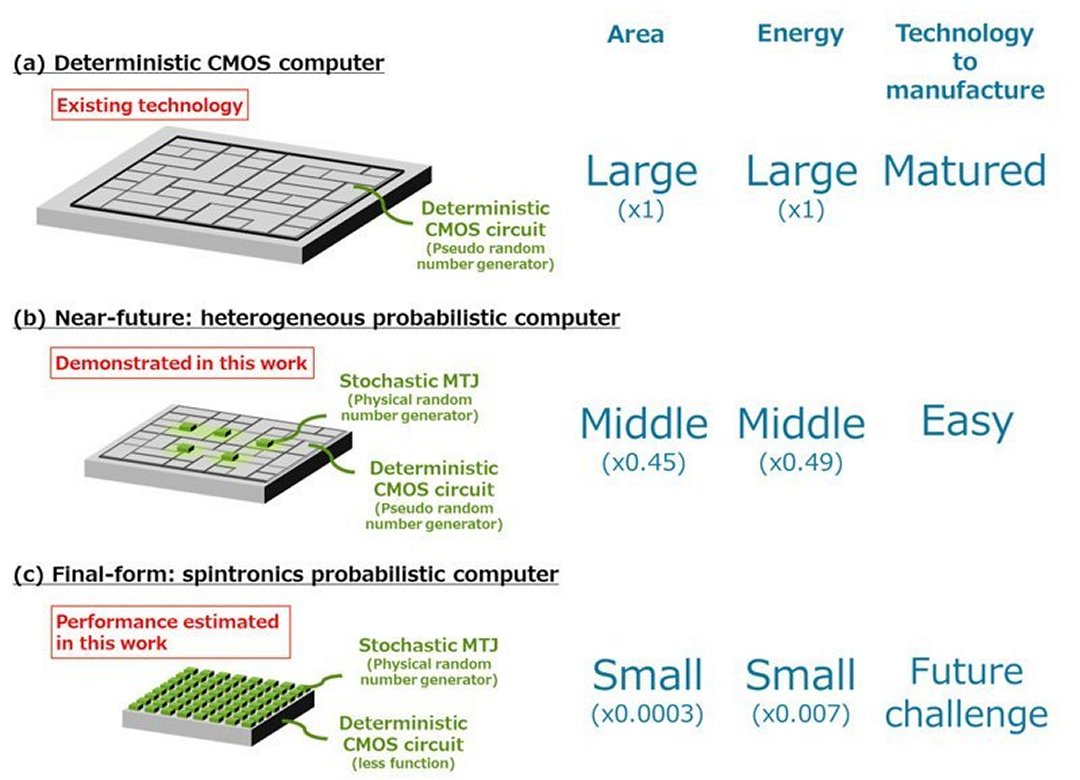

O computador probabilstico ideal para tarefas de IA, alm de ocupar menos espao e gastar mil vezes menos energia.

[Imagem: Nihal Sanjay Singh et al. – 10.1038/s41467-024-46645-6]

Ganhos de 10.000 vezes

A equipe usou nanoms para desenvolver junes de tneis magnticos estocsticos (sMTJs) no nvel dos componentes, o que permitiu construir os p-bits mais rpidos j feitos at hoje.

Agora, eles combinaram os bits probabilsticos sMTJs com chips programveis comuns, conhecidos como FPGA (Field Programmable Gate Arrays) para criar um prottipo CMOS + sMTJ, que a equipe chama de “verso heterognea de computador probabilstico para um futuro prximo”, em referncia ao nvel de prontido tecnolgica dos seus componentes spintrnicos.

O sistema foi projetado de tal forma que os bits probabilsticos spintrnicos, que j faziam parte da verso anterior, gerem um nmero aleatrio fsico que aciona os geradores de nmeros pseudo-aleatrios programados no circuito CMOS ou em um chip FPGA.

Os ganhos foram impressionantes: Para uma tarefa tpica de inteligncia artificial, o computador probabilstico alcanou uma reduo de quatro ordens de magnitude (10.000 vezes) na rea e uma reduo de trs ordens de magnitude (1.000 vezes) no consumo de energia, em comparao com os circuitos CMOS atuais. “Comparaes detalhadas em nvel de transstor revelam que p-bits baseados em sMTJs podem substituir at 10.000 transistores CMOS, enquanto dissipam duas ordens de magnitude menos energia,” escreveu a equipe.

Um esquema que ilustra a diferena dos computadores atuais, determinsticos e feitos com tecnologia CMOS: (a) da verso heterognea apresentada agora, (b) da verso que pode ser implementada em um futuro prximo e (c), da forma final de um computador probabilstico totalmente baseado na tecnologia spintrnica.

[Imagem: Nihal Sanjay Singh et al. – 10.1038/s41467-024-46645-6]

Futuro prximo

No por acaso, a computao probabilstica considerada uma ponte para a computao quntica, mas com a grande vantagem de que tudo j funciona temperatura ambiente.

“Nosso prottipo demonstrou que se pode alcanar um excelente desempenho computacional acionando geradores de nmeros pseudo-aleatrios em um circuito CMOS determinstico, com nmeros aleatrios fsicos gerados por um nmero limitado de nanomagnetos estocsticos,” detalhou o professor Shunsuke Fukami. “Especificamente falando, um nmero limitado de bits probabilsticos (p-bits) com uma juno de tnel magntico estocstico (s-MTJ) deve ser fabricado com uma tecnologia de integrao em um futuro prximo.”

Artigo: CMOS plus stochastic nanomagnets enabling heterogeneous computers for probabilistic inference and learning

Autores: Nihal Sanjay Singh, Keito Kobayashi, Qixuan Cao, Kemal Selcuk, Tianrui Hu, Shaila Niazi, Navid Anjum Aadit, Shun Kanai, Hideo Ohno, Shunsuke Fukami, Kerem Y. Camsari

Revista: Nature Communications

Vol.: 15, Article number: 2685

DOI: 10.1038/s41467-024-46645-6

Outras notcias sobre:

Mais tópicos

ENVIE UM COMENTÁRIO